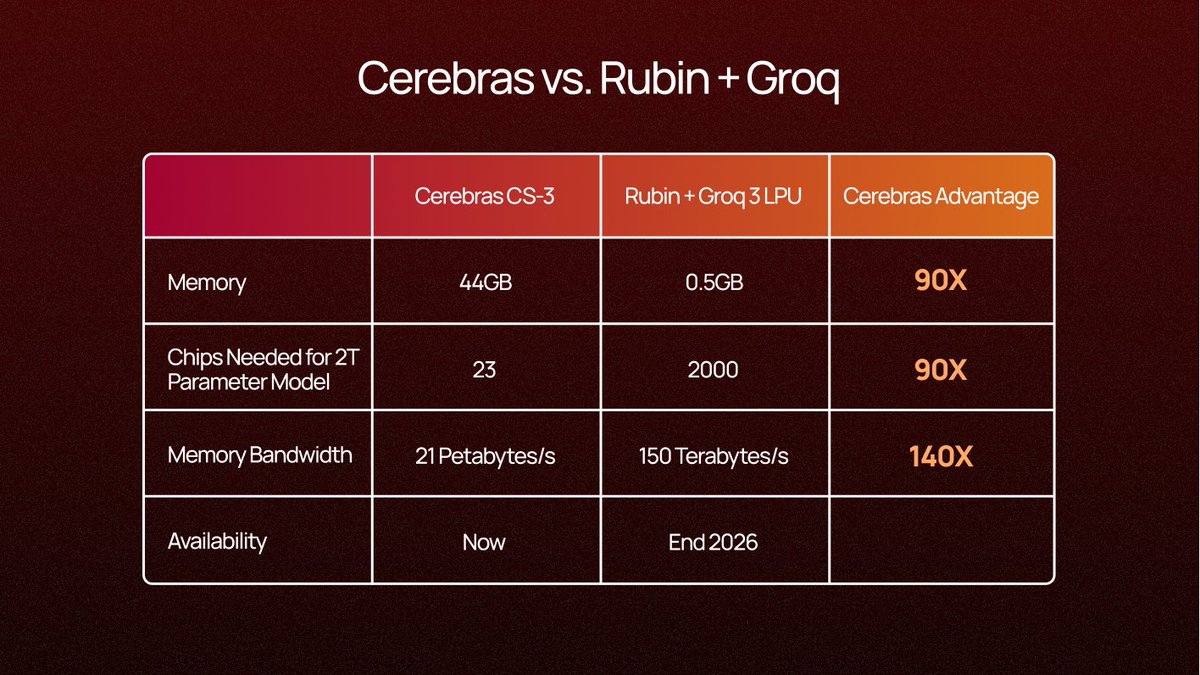

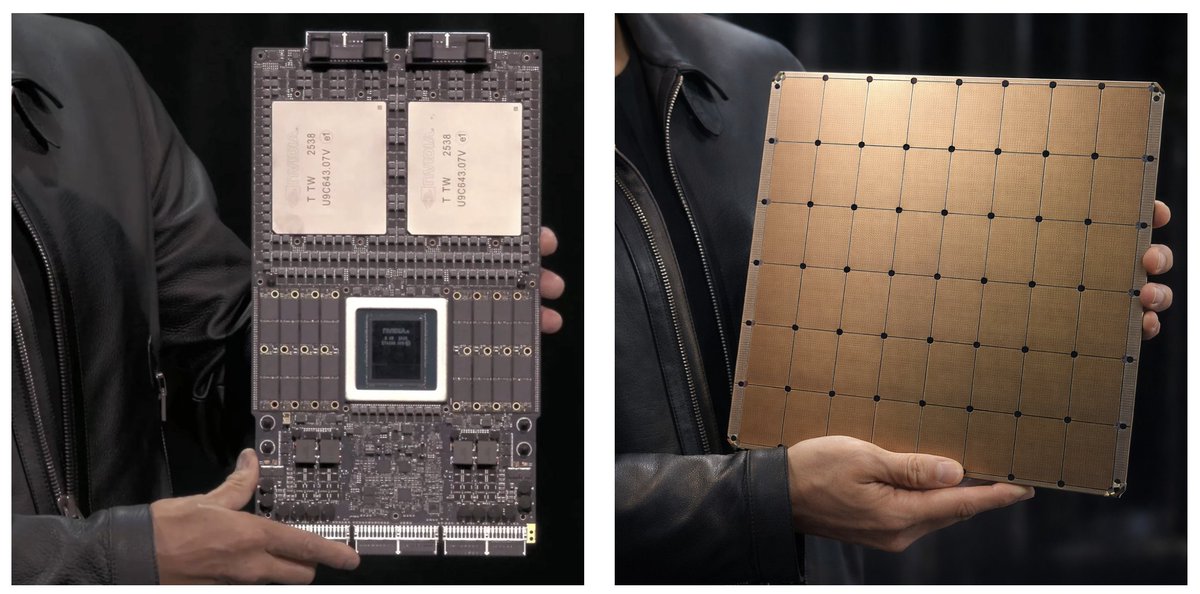

What is semiconductor yield? How does it work? Why did it define the semiconductor industry for 70 years? How did this problem get solved? And how does this impact developers? What Is Semiconductor Yield? When you manufacture chips, not every one comes out working. Some have defects. “Yield” is the percentage of chips from a manufacturing run that actually work. If you make 100 chips and 90 work, your yield is 90%. How Does Yield Work? Chips are made from silicon wafers – thin, circular discs about 12 inches in diameter. In a perfect world, every square millimeter of a wafer would be flawless. But that never happens. Every wafer has tiny random defects scattered across it. Chips are cut from these wafers. And any chip that lands on a defect is thrown away. The process of chip manufacturing looks a lot like your mother making cookies. Imagine your mom rolled out a circle of cookie dough 12 inches in diameter. Then when she wasn't looking, your brother threw a handful of peanut M&Ms into the air and they landed at random on the dough. Those M&Ms are flaws. Nobody can eat a cookie with a peanut M&M in it. So she has to throw away every cookie that has one. Now she gets out a small cookie cutter and stamps out cookies. Because the cookie cutter is small, the probability of hitting an M&M is low. And when a cookie does have one, there isn't much good dough surrounding it. Not much good dough is thrown away. The result: a lot of good cookies. They are small but there are a lot of them. On the other hand, if she uses a big cookie cutter, the probability of hitting an M&M is much larger. And when she throws that cookie away, she throws away a lot of good dough with it. The result: only a few cookies. They are big, but the 12 inch diameter circle of dough yielded only a few. This is exactly how chip manufacturing works. The cookie dough is a silicon wafer. The cookies are chips. Peanut M&Ms are flaws (because they are gross) Bigger chips hit more flaws. More good silicon gets thrown away. Smaller chips, like smaller cookies, are less likely to hit flaws. And when they do, less silicon is discarded. This is why big chips are disproportionately more expensive. This is also why people assumed that because there was no way to make a wafer without flaws, there was no way to make a chip the size of a wafer. Why Did This Define The Industry For 70 Years? In an ideal world, you'd build really big chips for many data center applications. Data moves incredibly fast on-chip. So if you keep the data and compute on-chip, your work takes less time, and uses less power. In AI, that manifests as super fast inference. But the moment data has to leave one chip and travel to another – through cables, switches, connectors, circuit boards – it slows down and uses more power. Lots of off-chip communication slows work, and, in AI, produces slow inference. Though everyone agreed they were faster, nobody could yield big chips. So the industry settled on a workaround: don't build one big chip. Build thousands of small ones and wire them together. Most AI data centers are built this way today. Thousands of little GPUs connected by cables, switches, and networks. It works. But you pay a price. Every connection adds latency. Every cable adds overhead. Every hop between chips slows things down. For 70 years, everyone accepted this as the only way. How Did Cerebras Solve the Yield Problem? In 2019, we solved the yield problem at @cerebras and brought the first wafer sized processor, wafer scale processor, to market. How did we do that? The answer came from studying a different kind of chip entirely. Memory. Memory is built with a different process. Memory chips are made up of millions of identical tiles, with redundant tiles woven throughout. In a memory chip, if a tile has a flaw in it, the chip doesn't get thrown away. The bad tile is shut down and one of the redundant ones is called into action. Memory chips weren't designed to avoid flaws, but rather to withstand them. They use redundancy to withstand flaws. And their yield is extraordinary. Our founders realized that if we could develop a compute architecture that looked like memory, that was built of hundreds of thousands of identical tiles, we too could use redundancy to withstand flaws. We could fail in place, and route around the failed tile, just as they do in memory (and interestingly as they do in data centers where they fail in place, route around, and keep going). This would enable us to yield a wafer scale processor. And today we are happy to compare our yields to GPUs, that are 1/58th our size. How Does This Impact Developers? The impact is simple and easy to see. Cerebras wafer scale processors are up to 15 times faster than @nvidia GPUs. And when your AI is fast, people use it more often, stay longer, and use it to solve more interesting problems.

→ View original post on X — @cerebras, 2026-04-02 16:07 UTC